Subtotal: $ 1.990

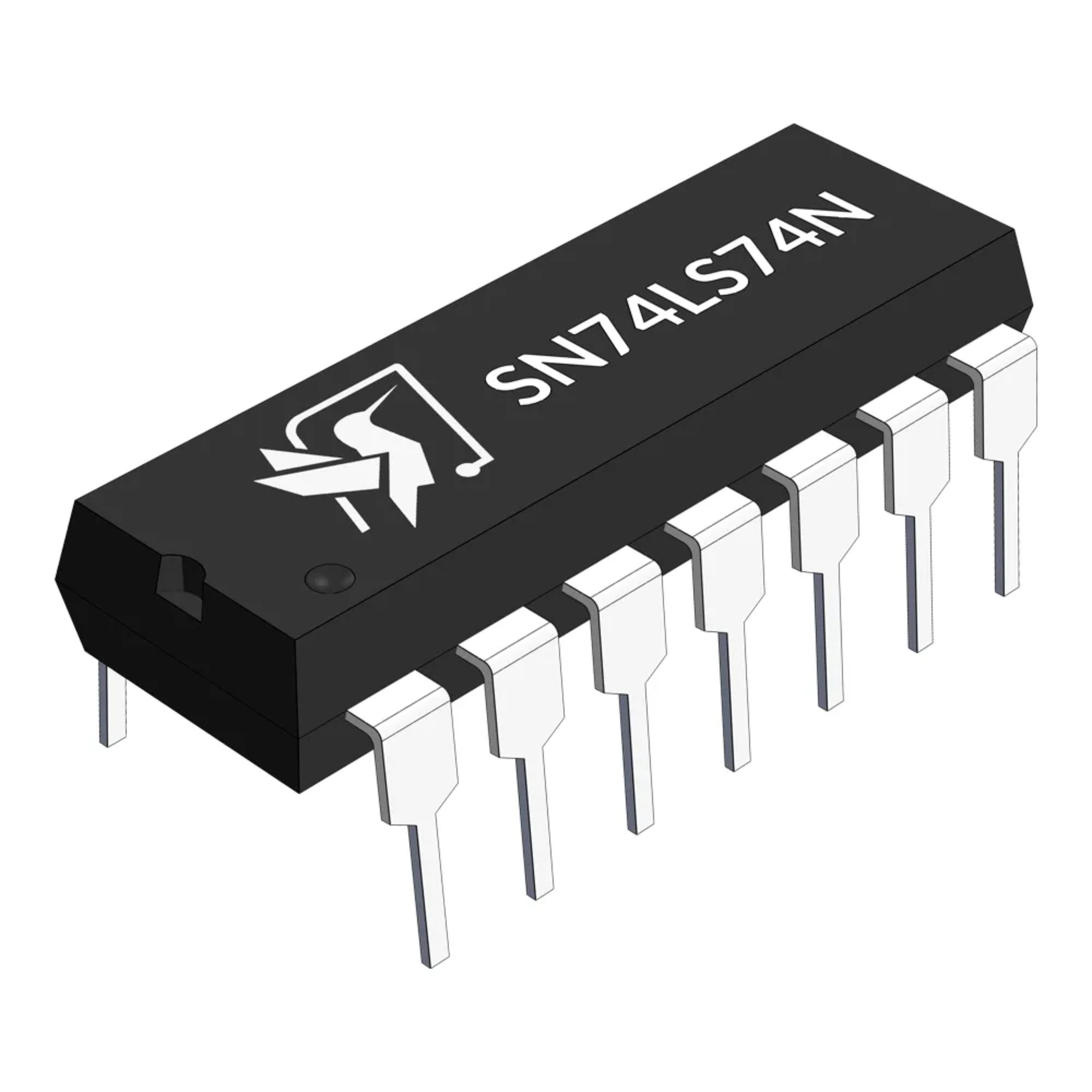

Circuito Integrado Flip Flop D 74LS74

$ 990 IVA incluido

El 74LS74 es un circuito integrado de la familia TTL que encapsula dos flip-flops D independientes de disparo por flanco positivo. Cada flip-flop cuenta con entradas asíncronas de preset y clear, lo que lo convierte en un componente versátil para el almacenamiento de un bit de datos, registros de desplazamiento y aplicaciones de retardo de señal en sistemas digitales. Es ideal para mantener un estado lógico de forma estable y sincronizada con la señal de reloj.

✅ Boleta y factura

- 🚚 Ver política de despachos debajo de la descripción

Hay existencias

📃 ¿Necesitas una Cotizacion? ¿Comprar para universidades, mercado publico o compra ágil? ¡Contáctanos!.

SKU: GK3-7

Categorías: Circuitos Integrados (IC), IC y Componentes (Circuitos Integrados)

Descripción

El 74LS74, un componente fundamental de la familia lógica TTL (Transistor-Transistor Logic) de baja potencia Schottky, es un circuito integrado que contiene **dos flip-flops D independientes y duales**. Cada flip-flop se caracteriza por su **disparo por flanco positivo del reloj**, lo que significa que los datos presentes en la entrada ‘D’ se transfieren a la salida ‘Q’ en la transición ascendente (de BAJO a ALTO) del pulso de reloj.

Este IC es ampliamente utilizado para el almacenamiento de un solo bit de datos, la construcción de registros de desplazamiento, contadores síncronos, divisores de frecuencia, y para la sincronización de señales en sistemas digitales. Sus entradas asíncronas de **preset (PRE’) y clear (CLR’)**, ambas activas en bajo, permiten establecer (SET) o borrar (RESET) el estado del flip-flop independientemente de la señal de reloj y la entrada ‘D’.

El 74LS74 ofrece una solución robusta y confiable para la lógica secuencial, proporcionando estabilidad en el almacenamiento de datos. Su encapsulado **DIP de 14 pines** (Dual In-line Package) facilita su montaje y depuración en prototipos y diseños finales.

Especificaciones Máximas

| Parámetro | Valor |

|---|---|

| Voltaje de alimentación (Vcc) | 4.75 V a 5.25 V (típico 5V) |

| Voltaje de entrada (VI) | 5.5 V |

| Corriente de salida (IOH / IOL) | -0.4 mA / 8 mA |

| Temperatura de operación | 0°C a +70°C |

| Temperatura de almacenamiento | -65°C a +150°C |

Características Térmicas

| Característica | Valor Típico |

|---|---|

| Disipación de potencia por flip-flop | 10 mW |

Características Adicionales

| Característica | Valor Típico |

|---|---|

| Frecuencia máxima de reloj (fclk) | 30 MHz |

| Retardo de propagación (tPLH/tPHL, CLK a Q) | 25 ns |

| Retardo de propagación (tPLH/tPHL, PRE’/CLR’ a Q) | 20 ns |

| Ancho de pulso de reloj (tW) | 20 ns |

| Tiempo de setup (tSU, D a CLK) | 20 ns |

| Tiempo de hold (tH, D de CLK) | 5 ns |

| Encapsulado | DIP-14 |

| Número de flip-flops | 2 (duales) |

| Tipo de disparo | Flanco positivo (LOW-HIGH) |

Preguntas Frecuentes

¿Qué es un flip-flop D y cómo se diferencia de un latch D?

Un flip-flop D (Data Flip-Flop) es un elemento de memoria digital que almacena el valor presente en su entrada ‘D’ solo en el momento de un flanco activo de reloj (en el caso del 74LS74, el flanco positivo). A diferencia de un latch D, cuya salida puede cambiar siempre que el reloj esté en un nivel alto, un flip-flop D es sensible solo a la transición del reloj, lo que garantiza una operación más sincronizada y libre de riesgos de transparencia.

¿Cuál es la función de las entradas PRE’ (Preset) y CLR’ (Clear) en el 74LS74?

Las entradas PRE’ (Preset) y CLR’ (Clear) son entradas asíncronas de control, lo que significa que actúan independientemente del pulso de reloj y de la entrada ‘D’. Ambas son activas en bajo. Si PRE’ se pone a bajo, la salida Q se fuerza a ALTO. Si CLR’ se pone a bajo, la salida Q se fuerza a BAJO. Si ambas se ponen a bajo simultáneamente, se produce un estado inválido o indeterminado en Q y Q’. Para el funcionamiento normal del flip-flop, ambas entradas deben mantenerse en ALTO.

¿Cómo se utiliza el 74LS74 en un registro de desplazamiento?

El 74LS74 es un componente clave para construir registros de desplazamiento. Conectando la salida Q de un flip-flop a la entrada D del siguiente flip-flop en serie, y aplicando un reloj común a todos, se puede desplazar datos bit a bit a través de la cadena con cada pulso de reloj. Esto es útil para convertir datos de serie a paralelo o viceversa, o para crear secuencias de bits.

¿Qué otros circuitos integrados son equivalentes o alternativas al 74LS74?

Existen varias alternativas dependiendo de la tecnología y los requisitos de velocidad/consumo: el 74HC74 (versión CMOS de alta velocidad, compatible con TTL en pines), el 74HCT74 (versión CMOS de alta velocidad, directamente compatible en niveles lógicos con TTL), 74F74 (TTL de alta velocidad), y 74ALS74 (TTL Schottky de baja potencia avanzada). Otros flip-flops D de la serie 7400, como el 74LS175 (cuádruple flip-flop D con clear común), también pueden ser considerados.

¿Se puede utilizar el 74LS74 para dividir una frecuencia de reloj?

Sí, un flip-flop D se puede configurar fácilmente como un divisor de frecuencia de «división por 2». Esto se logra conectando la salida complementaria Q’ de un flip-flop D a su propia entrada D, y aplicando la señal de reloj original a la entrada CLK. Cada dos pulsos de la señal de reloj de entrada, la salida Q cambiará de estado, generando así una señal con la mitad de la frecuencia. Dado que el 74LS74 contiene dos flip-flops, puede usarse para una división por 2, por 4 (cascando ambos flip-flops) o para generar señales de reloj con fases divididas.

Valoraciones (0)

Sé el primero en valorar “Circuito Integrado Flip Flop D 74LS74” Cancelar la respuesta

Politicas de compra

- La boleta o factura se genera automáticamente en cada compra, utilizando los datos que ingreses al realizar tu pedido.

- Si compra antes de las 13:00 hrs, despachamos su pedido desde origen el mismo día.

- El costo de envío se calcula automáticamente antes de finalizar el pedido, en función de las dimensiones, peso y comuna/ciudad de destino. Trabajamos con Chilexpress y Bluexpress.

- Si al finalizar el pedido selecciona envío gratis, debe considerar que se aplicarán las políticas de transporte correspondientes al servicio contratado.

- El tiempo de entrega se especifica según cada ciudad, comuna y el método de envío seleccionado. Sin perjuicio de que el servicio de envío se pueda retrasar:

Despacho al día hábil siguiente para envíos a: Santiago centro, Huechuraba, Independencia, La Cisterna, La Reina, Las Condes, Macul, Maipú, Ñuñoa, Pedro Aguirre Cerda, Providencia, Pudahuel, Quinta Normal, Recoleta, Renca, Talca, Talcahuano, Vitacura, Conchalí, Estación Central, Concepción, Chillán, Cerro Navia, Cerrillos, Quilicura.

Para otras comunas, el tiempo de entrega se determinará según el servicio de envío (Chilexpress o Bluexpress) hacia: Valparaíso, San Bernardo, Peñalolén, Temuco, Arica, Puerto Montt, La Serena, Coquimbo, Rancagua, Calama, Iquique, Quilpué, Los Ángeles, Punta Arenas, Curicó, Osorno, Castro, Coronel, Ovalle, San Antonio, Buin, Lampa, Melipilla, Los Andes, San Felipe, La Ligua, Rengo, San Vicente de Tagua Tagua, San Fernando, Santa Cruz, Graneros, Lautaro, Loncoche, Villarrica, Lanco, Panguipulli, Río Bueno, Paillaco, Chiguayante, Hualpén, Tocopilla, Quellón, Molina, Curanilahue, Lota, Angol, Penco.

Productos relacionados

Cableado y Conexionado

$ 300 IVA incluido

¡Oferta!

Cableado y Conexionado

$ 250 – $ 400 IVA incluido

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Cables hembra-hembra 40 piezas 20cm

Cables hembra-hembra 40 piezas 20cm

Valoraciones

No hay valoraciones aún.